# Fraunhofer Center

Center Nanoelektronische Technologien

# Jahresbericht 2007

annual report

chnology & Know-how

Equipment

Silizum

Wafer

Frauhofer Gesellschaft

MIKROelektronik NANOtechnologie

Forschung Chips

Research & Development

Silicon Saxony

Dresden

Puplic Private Partnership

Halbleiter

# Jahresbericht 2007 annual report

Fraunhofer-Center Nanoelektronische Technologien Koenigsbruecker Str. 180 01099 Dresden, Germany

+49 (0) 351 / 2607 3001 www.cnt.fraunhofer.de

Prof. Dr. Peter Kücher Leiter der Einrichtung

#### Vorwort

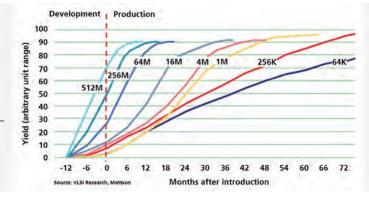

"Innovation durch Kooperation" - lautet das Motto am Fraunhofer-Center Nanoelektronische Technologien (CNT) in Dresden. Mit der Fraunhofer-Gesellschaft haben die in der Halbleiterbranche führenden Hersteller für Speicher und Prozessoren in Dresden, Qimonda und Advanced Micro Devices (AMD) eine gemeinsame Forschungseinrichtung auf den Weg gebracht. Ziel der Einrichtung ist es, schnelle und fertigungsnahe Lösungsansätze zu entwickeln, welche direkt in der Fertigung umgesetzt werden können. Hierzu bietet Dresden, im Herzen des sogenannten "Silicon Saxony" die idealen Vorraussetzungen, da sich an diesem Standort traditionell das Wissen der Branche mit dem Innovationsdrang der Hersteller bündelt. In Dresden, als einem der wichtigsten Standorte für Hochtechnologie in Deutschland, befinden sich neben elf Fraunhofer Instituten, sechs Max-Planck- und Leibniz Institute, die Technische Universität und die Fachhochschule Dresden. Diese tragen neben der Forschung wesentlich zur Ausbildung des wissenschaftlichen Nachwuchses bei. Im Bereich Halbleiter arbeiten heute bereits mehr als 40.000 Menschen direkt oder indirekt in der Region.

Seit der Gründung im Mai 2005 wird am Fraunhofer-Center Nanoelektronische Technologien an innovativen Materialien, Prozessen und Strukturen geforscht. Mit Hilfe neuer Lösungsansätze gilt es, den Erfordernissen der Industrie nach sinkenden Kosten und steigender Effizienz gerecht zu werden und dabei Entwicklungen bei Technologien, Prozessen und Anlagen zu implementieren.

Bis zum Ende des Jahres 2007 wurden in unserem Haus umfangreiche Projekte mit den Industriepartnern sowie anderen Instituten und Forschungseinrichtungen durchgeführt.

Der Übergang von der Mikro- zur Nanoelektronik stellt eine große Herausforderung sowohl für Forschung und Entwicklung als auch Fertigung dar, welche zahlreiche neue Forschungsgebiete erschließt, aber auch neue Formen der Zusammenarbeit erfordert. Wesentlich für den Erfolg aller Beteiligten im internationalen Wettbewerb, ist das schnelle Umsetzen der effizientesten Konzepte und die Zusammenarbeit in kompetenten, regionalen und internationalen Clustern.

Diese Broschüre soll Ihnen einen kleinen Einblick in die Entwicklungen am Fraunhofer CNT seit seiner Gründung geben. Ich hoffe, wir können Ihnen beim Lesen etwas von der Faszination der Forschung an den atomaren Grenzen der Elektronik vermitteln!

Peter Kücher

### Preface

"Innovation through cooperation" is our mission statement at the Fraunhofer-Center for Nanoelectronic Technologies (CNT) in Dresden. Together with the Fraunhofer-Gesellschaft, Qimonda and Advanced Micro Devices (AMD) established a joint research center. Both companies are leading manufacturers for memory and processor devices of the semiconductor industry in Dresden. The aim of the center is to develop fast and production-related solutions, which can be directly implemented into industrial production. Dresden, in the heart of the so-called "Silicon Saxony", offers ideal conditions to link scientific expertise in the field of semiconductors with manufacturers' innovation objectives. In Dresden, as one of the main locations for high technology in Germany, eleven Fraunhofer institutes, six Max-Planck and Leibniz institutes, the Technical University and the University of Applied Science Dresden can be found. Besides research. they contribute to the education of young scientists. In the local region, more than 40,000 people are currently working directly or indirectly in semiconductor industry of the region.

Established in May 2005, the Fraunhofer Center Nanoelectronic Technologies is investigating innovative materials, processes and structures. New approaches are essential to satisfy the industrial requirements for cost reduction and increasing efficiency with implementing developments of technologies, processes and systems.

The transition from micro to nano-electronics is a major challenge for research and development as well as manufacturing. It opens a number of new research areas and new forms of cooperation. The rapid implementation of the most effective solutions and the cooperation in national and international clusters is substantial for all participants to stand the international competition.

By the end of 2007, numerous projects with industry partners, research institutes and universities have been progressed in our house.

This brochure shall give you a brief insight into the ongoing developments at the Fraunhofer CNT since its formation. I hope by reading this brochure you can share with us the fascination of doing research at the atomic scale of electronics.

Peter Kuecher

### INHALT

### CONTENT

| Fraunhofer-Center Nanoelektronische Technologien<br>Fraunhofer-Center for Nanoelectronic Technologies |    |

|-------------------------------------------------------------------------------------------------------|----|

| Überblick<br>Overview                                                                                 | 09 |

| Forschungsschwerpunkte - ausgewählte Bereiche<br>Focus Areas - Selected Examples                      | 19 |

| Innovative Prozesse & Materialien Innovative Processes and Materials                                  | 20 |

| Metrologie & Analytik<br>Metrology & Analytic                                                         | 32 |

| Daten & Fakten<br>Facts & Figures                                                                     | 41 |

### Fraunhofer-Center Nanoelektronische Technologien

### Überblick

Overview

| Das Institut im Profil Herausforderungen der Halbleiterindustrie im Nanozeitalter The institute's profile Challenges of the semiconductor industry in the Nano Era                                                          | 10 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Zusammenarbeit zwischen Forschung und industrieller Fertigung Das Konzept - Public Private Partnership Cooperation between research and industrial production Public Private Partnership, the concept of the Fraunhofer CNT | 11 |

| Die Fraunhofer-Gesellschaft<br>Forschung im Verbund Mikroelektronik (VµE)<br>The Fraunhofer-Gesellschaft<br>Research in the Fraunhofer Group Microelectronics                                                               | 12 |

| Das Institut in Zahlen The institute numbers                                                                                                                                                                                | 15 |

| Die Kompentenzgebiete des Fraunhofer CNT The competence areas of the Fraunhofer CNT                                                                                                                                         | 16 |

| Projektübersicht nach Partnern und Fördermittelgebern 2007<br>Project overview by partners and funding authorities 2007                                                                                                     | 17 |

### Das Institut im Profil

Herausforderungen der Halbleiterindustrie im Nanozeitalter

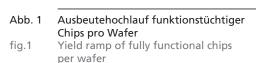

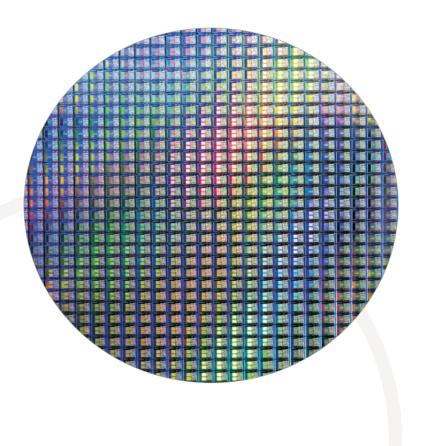

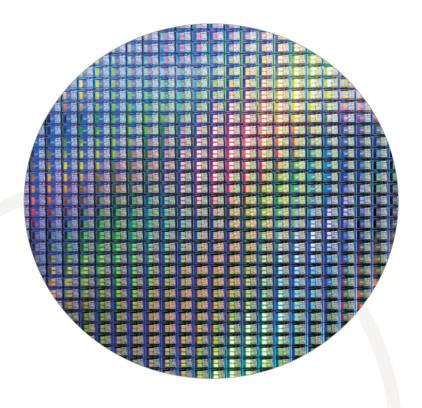

Vor etwa 5 Jahren galt in der Chipindustrie eine Dichte von 55 Mio Transistoren auf einer Fläche von 1cm<sup>2</sup> unterzubringen noch als Spitzenleistung. Heute erreichen moderne Prozessoren die 3 bis 10fache Anzahl von Transistoren auf der gleichen Fläche. Die Halbleiterindustrie befindet sich damit in der Skalierung von Strukturen bereits weit unter einer Größe von 100 nm – dem Bereich der Nanoelektronik. Neben dem Erreichen technologischer Grenzen im atomaren Bereich, stellt die Beherrschung der Fertigung auf Silizium-Wafern mit einem Durchmesser von 300 mm mit schnellem Ausbeutehochlauf eine große Herausforderung dar (Abb. 1). Für den Erfolg und das weitere Wachstum der Branche ist eine Kostensenkung von ca. 30% pro Jahr, bei gleichzeitiger Verdoppelung der Funktionalität alle 2 Jahre notwendig. Diese Entwicklung wurde von Gordon Moore bereits Anfang der 60iger Jahre prognostiziert.

Um sowohl die technologischen als auch die fertigungsnahen Herausforderungen der Skalierung von Prozessen und Bauteilen bei gleichzeitig hoher Ausbeute zu beherrschen, müssen neue Kooperationskonzepte zwischen Forschungseinrichtungen und den Halbleiterherstellern erprobt werden. Kürzere Produktlebenszyklen sowie größere Produktvielfalt mit ständig steigenden Anforderungen und der Notwendigkeit die Produktionskosten zu senken, erfordern neue Konzepte für die schnellere Implementierung innovativer Entwicklungsschritte beim Übergang von Entwicklung in die Fertigung.

Neben einer Verkleinerung der Strukturen wird in der Industrie ebenso an der Umsetzung der Erkenntnisse direkt in der Fertigung geforscht. Zu diesem Zweck haben die Halbleiterhersteller Qimonda und Advanced Micro Devices mit der Fraunhofer-Gesellschaft im Mai 2005 das Fraunhofer-Center Nanoelektronische Technologien in Dresden gegründet. Unter dem Dach einer Public Private Partnership werden an diesem Standort die Synergieeffekte von Wissenschaft und Wirtschaft genutzt. In diesem neuen Modell der Zusammenarbeit wird es möglich, direkt an den Herstellungsschritten der Industriepartner zu forschen und die Effektivität der Ergebnisse zu testen – entsprechend der Mission "Docking Research into Manufacturing".

### The institute's profile

Challenges of the semiconductor industry in the Nano Era

About 5 years ago, a number of 55 million transistors placed on an area of 1cm<sup>2</sup> meant more than excellence in the chip industry. Today, modern processors have a 3 to 10 times higher number of transistors on the same area. In the semiconductor industry the structures' are already below a size of 100 nm - the era of nanoelectronics. Besides reaching the technological limits in the atomic scale, another major challenge is the fast process ramp to high yield on silicon wafers with a diameter of 300 mm (fig. 1). For the success and the continued growth of the industry a cost reduction of about 30% per year is required, while the functionality needs to be doubled every two years. This development has been anticipated by Gordon Moore at the beginning of the 60s.

To control the technical and production related challenges of scaling processes and components, new collaboration concepts between research and the semiconductor industry by ramping to high volume in parallel have to be established. Shorter product life cycles, greater product variety, increasing demands and the need to reduce production costs require new concepts for faster implementation of innovative development steps.

Besides shrinking the technology, the industry is also interested in transferring technical expertise directly into the manufacturing. Therefore, the semiconductor manufacturers Qimonda and Advanced Micro Devices as well as the Fraunhofer-Gesellschaft founded the Fraunhofer Center for Nanoelectronic Technologies in Dresden, in May 2005. With the framework of a Public Private Partnership the synergistic effect between science and industry will be utilized. Within that model of collaboration, it is possible to study process steps and to test the effectiveness of solutions in-line - according to our mission "Docking Research into Manufacturing".

### Zusammenarbeit zwischen Forschung und industrieller Fertigung

Das Konzept - Public Private Partnership

In Dresden, als weltweit einzigem Standort für eine Volumen Speicher- als auch Prozessorenfertigung, wurde ein neuer Weg eingeschlagen, um in einer Kooperation gemeinsam Wissen zu schaffen und dieses in einer Fertigungsumgebung umzusetzen.

Die Fraunhofer-Gesellschaft, Advanced Micro Devices (AMD) und Qimonda Dresden etablierten daher in Dresden eine Forschungsplattform auf dem Gelände von Qimonda mit direkter Anbindung zu den weltweit führenden 300 mm Fertigungslinien. In einer öffentlich privaten Partnerschaft betreibt die Fraunhofer-Gesellschaft den Reinraum und bringt über die Beteiligung anderer Institute, z.B. aus dem Verbund Mikroelektronik, zusätzliches Know-how ein. Die Technische Universität Dresden ist als beratender Partner an der Kooperation beteiligt und arbeitet ebenso wie verschiedene europäische Universitäten und Forschungseinrichtungen u.a. CEA / Leti und IMEC als Partner in Projekten mit.

### Cooperation between research and industrial production

The concept - Public Private Partnership

In Dresden, a worldwide exclusive location for volume memory as well as processor production, a new path is gone to create knowledge in a joint cooperation and to implement this knowledge into a production line.

Therefore, the Fraunhofer-Gesellschaft, Advanced Micro Devices (AMD) and Qimonda Dresden established a research platform at the Qimonda area with direct connections to the world's leading 300 mm production lines in Dresden. Within the scope of a public private partnership, the Fraunhofer-Gesellschaft operates a clean room and imparts knowledge by involving other institutions, such as the Fraunhofer Group Microelectronics. The Dresden University of Technology represents a consultant partner within the cooperation and collaborates in projects similar to various European universities and research institutions, i.e. CEA / Leti and IMEC.

Der Freistaat Sachsen und das Bundesministerium für Bildung und Forschung fördern die Einrichtung mit 80 Mio € für die Grundausstattung, sowie weiteren 85 Mio € für Forschungsprojekte in den Jahren 2005 – 2011, bei einem Forschungsvolumen von 170 Mio €. Zu diesem Zweck betreibt das Fraunhofer CNT Reinraumflächen in der Nähe der Entwicklungs- und Fertigungslinie von Qimonda. Für ihre Arbeiten stehen den Wissenschaftlern im Reinraumgebäude von Qimonda Dresden über 800m² Fläche der Klasse ISO6 bzw. ISO3 mit Mess- und Prozessgeräten zur Verfügung. Weiterhin können fast 170m² Laborflächen außerhalb des Reinraums genutzt werden.

Kern des Konzepts ist es, teilprozessierte Wafer aus den Fertigungslinien der Industriepartner für die gemeinsame Forschung zu nutzen und damit die Investitionen für die Linie zu minimieren, sowie gleichzeitig ein schnelles Lernen für alle Beteiligten zu ermöglichen.

The Free State of Saxony and the German Federal Ministry for Education and Research are supporting the institution by funding € 80 million for the basic facilities and € 85 million for running research projects for the years 2005-2011, by reaching a research volume of € 170 million.

For these purposes, the Fraunhofer CNT operates a clean room facility next to the development and production lines of Qimonda. For scientific work, 800 m² cleanroom area of class ISO6 or ISO3 with analyzing and process equipment is available in the clean room building of Qimonda. Apart from the cleanroom, another 170 m² laboratory space can be used.

Core of the concept is to use partly processed wafers out of the production lines of the industrial partners for joint research. On one hand, this is done to reduce investment costs, and on the other hand, to allow faster learning for all partners.

### Die Fraunhofer-Gesellschaft Forschung im Verbund Mikroelektronik

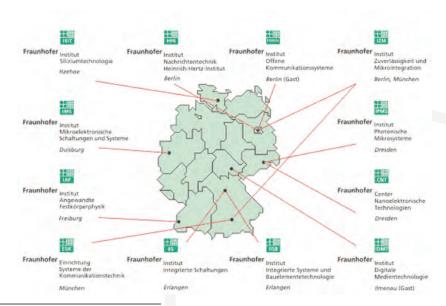

Die Fraunhofer-Gesellschaft ist mit bundesweit 60 Instituten und über 12.500 Mitarbeitern in 2007 eine der führenden Organisationen für angewandte Forschung in Europa. Seit 1996 haben sich Fraunhofer-Institute mit ergänzenden Forschungsschwerpunkten zu thematischen Verbünden zusammengeschlossen, um gemeinsam effektiver technische Innovationen für die Kunden zu entwickeln. Dabei ist das Fraunhofer CNT Teil des Verbundes für Mikroelektronik VµE, welcher 12 Institute mit Forschungsaktivitäten im Bereich der Mikroelektronik vereint. Die Mitglieder des Verbundes profitieren von der breiten Technologiekompetenz und dem Produkt Know-how unter dem Dach der Fraunhofer-Gesellschaft.

# The Fraunhofer-Gesellschaft research in the Fraunhofer Group Microelectronics

The Fraunhofer-Gesellschaft, with its 60 institutes and currently more than 12,500 employees nationwide, is one of the leading organizations for applied research in Europe. Since 1996, Fraunhofer institutes with complementary research focuses work together in networks to effectively develop technical innovations for customers.

The Fraunhofer CNT is part of the Group Microelectronics  $V\mu E$ , which involves 12 research institutions with activities in the field of microelectronics. The members of that alliance benefit from the broad technology expertise and product know-how under the roof of the Fraunhofer-Gesellschaft.

Das Fraunhofer CNT ist dem Geschäftsfeld "More Moore and Beyond CMOS" zuzuordnen. Ziel des Verbundes ist es, sich in diesem Arbeitsbereich eine internationale Spitzenposition zu sichern, um so die wirtschaftlichen Erfolge der Industrieauftraggeber sicherzustellen. Mit dem Center Nanoelektronische Technologien bietet sich für die Fraunhofer-Gesellschaft eine neue, hervorragend ausgestattete Forschungs- und Entwicklungsplattform auf der Basis von 300 mm Silizium-Wafern für die Zusammenarbeit mit IC Herstellern, die im Hochvolumenmarkt mit Bauelementen für Speicher oder Prozessoren tätig sind.

The Fraunhofer CNT is related to the Business Area "More Moore and Beyond CMOS". Aim of the alliance is to ensure an international top position in the working field of microelectronics and to guarantee the economic success of the cooperation partners.

With the Center for Nanoelectronic Technologies, the Fraunhofer-Gesellschaft offers a new and fully equipped research and development platform based on 300 mm silicon wafers for cooperation with IC manufacturers active in the high-volume memory and processor device market.

Die FuE-Aktivitäten der Fraunhofer-Gesellschaft im Bereich der CMOS Technologien umfassen u.a. die folgende Bereiche:

- Verfahren und Simulationen zur Herstellung von perfekten Kristallen

- Entwicklung flacher Dotierungen für schnellste Schaltelemente

- Einsatz neuer Materialien mit maßgeschneiderten Eigenschaften

- Erzeugung verspannter Siliziumschichten und Einsatz von SiGe für high-performance-CMOS-Bausteine und optische Anwendungen

- Materialsysteme für neuartige Speichertechnologien

- Material- und Verfahrensentwicklung für Isolationsmaterialien mit niedriger Dielektrizitätskonstante

- Verfahren zur Herstellung von ultradünnen Barriere- und Kontaktschichten

Dies ist eine Auswahl der breiten Kompetenzspektren in der Fraunhofer-Gesellschaft, welche in die Projekte mit den Industriepartnern des Fraunhofer CNT eingebracht werden können.

The research and development activities in the area of CMOS technologies include following areas:

- Procedures and simulation for the production of perfect crystals

- Development of flat doping implantation for very fast circuits

- Application of new materials with tailored properties

- Production of stressed silicon layers and the use of SiGe for high-performance CMOS devices and optical applications

- Material systems for advanced storage technologies

- Material and process development for insulating materials with low dielectric constant

- Methods for manufacturing ultra-thin barrier and contact layers

This is a selection of the wide range of expertise of the Fraunhofer-Gesellschaft, which can be inserted into the projects of Fraunhofer CNT with the industrial partners.

Institute im Fraunhofer Verbund für Mikroelektronik Institutes at the Fraunhofer Group Microelectronic

### Das Institut in Zahlen

#### Mitarbeiterentwicklung

Die Anzahl der beschäftigten Mitarbeiter des Fraunhofer CNT ist seit Beginn kontinuierlich gestiegen. Zum Ende des Jahres 2007 bestand das Team aus 26 Wissenschaftlern und 8 Mitarbeitern im Verwaltungs- und Managementbereich.

Zusammen mit den ~65 Mitarbeitern der Industriepartner, anderer Institute und Universitäten sind zurzeit etwa 100 Beschäftigte im Rahmen der Projekte am Fraunhofer CNT tätig

### The institute in numbers

### Employee development

The number of employees at the Fraunhofer CNT is continuously growing from the beginning. At the end of 2007, the team consisted of 26 scientists and 8 employees in administrative and management departments.

Together with those ~65 employees, who are contracted by the industrial partners, other institutes or Universities and work on Fraunhofer CNT projects, currently about 100 staff members are involved in the Fraunhofer CNT business.

### Aufwendungen und Erträge im Jahr 2007

Revenue and Expenses in the year 2007

|                                                      | in T € | in %  |

|------------------------------------------------------|--------|-------|

| Jahresbudget 2007<br>2007 annual budget              | 12.426 |       |

| Aufwendungen<br>Expenses                             |        |       |

| Personalaufwendungen<br>Personal Expenses            | 926    | 7,5%  |

| Sachaufwendungen<br>Nonpersonal Expenses             | 11.500 | 92,5% |

| Erträge<br>Revenue                                   |        |       |

| FuE Erträge Industrie<br>R&D Revenue industry        | 6.814  | 54,8% |

| Sonstige Erträge Industrie<br>misc. Revenue industry | 5.561  | 44,8% |

| Grundfinanzierung<br>basic funding                   | 51     | 0,4%  |

|                                                      |        |       |

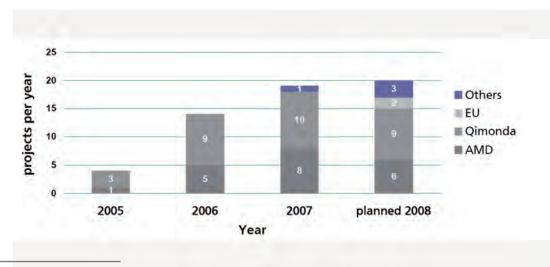

### Projekte

2007 wurden im Fraunhofer CNT 19 Projekte, darunter 13 FuE-Projekte durchgeführt. Im Rahmen der öffentlich-finanzierten Forschungsprojekte mit den Industriepartnern wurden 10 Projekte gemeinsam mit Qimonda Dresden und 8 Projekte mit AMD verwirklicht. Eines von diesen wurde auch in Kooperation beider Industriepartner realisiert. (Abb. 1)

### **Projects**

In 2007, the institute participated in 19 projects, thereof 13 R&D projects. 10 projects have been in collaboration with Qimonda, while 8 projects have been in collaboration with AMD.

One of the projects is going to be performed in cooperaton by the industry partners. (fig. 1)

Abb. 1 Projektüberblick pro Jahr fig. 1 project overview per year

### Anlagen

Das Fraunhofer CNT verfügt über 40 Anlagen zur Prozessierung von 300 mm Siliziumscheiben in Abscheide- und Ätzanlagen sowie Anlagen für die Wärmebehandlung bei Hochtemperaturen und Inspektions- und Analysegeräten zum Bestimmen von Defekten und Messen der Schichteigenschaften. Durch die gute Zusammenarbeit in einer professionellen, industriellen Infrastruktur konnten die Anlagen termingerecht installiert, charakterisiert und für die Forschungsarbeiten bereitgestellt werden. Die Geräte ermöglichen die Prozessierung von Siliziumscheiben (Wafern) von 300 mm Durchmesser, mit neuen und etablierten Methoden als auch innovativen Materialkombinationen. Mit mehr als 12 unterschiedlichen Charakterisierungsverfahren können Eigenschaften kristalliner Schichtsysteme analysiert oder tiefenaufgelöste Elementzusammensetzung durchgeführt werden.

Derzeit werden im Fraunhofer CNT mehr als 5.000 Wafer, in verschiedenen Analyse- & Prozessschritten bewegt. Dabei beträgt die durchschnittliche Verweildauer von integrierten Wafern weniger als 14 Tage.

### Equipment

The Fraunhofer CNT owns approx. 40 tools for processing 300 mm silicon wafers. Those tools are divided into deposition and etching systems, equipment for heat treatment at high temperatures, as well as inspecting and analyzing tools for defect detection and measurement of material properties. Through close cooperation in a professional, industrial infrastructure, the equipment could be installed, qualified and hooked up for research in time.

The equipment allows the processing of 300 mm wafers using either state-of-the-art or research methods as well as innovative material combinations. With more than 12 different characterization methods, material properties and depth profiles of thin films can be evaluated.

At this time, more then 5.000 wafers are moved in different steps of analysis and processes. The average cycle time thereby is in the range of 14 days.

Anlage im Reinraum des Fraunhofer CNT Equipment at the Fraunhofer CNT clean room

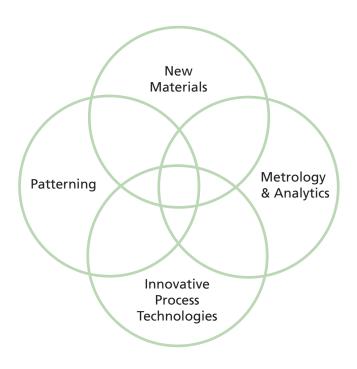

### Die Kompetenzgebiete des Fraunhofer CNT

Der Forschungs- und Projektarbeiten am Fraunhofer CNT werden in 4 Kompentenzgebiete unterteilt. In den entsprechenden Arbeitsgruppen bündelt sich das Wissen und technische Know-how der Wissenschaftler aus Industrie und Forschungseinrichtungen.

### Competence Areas of the Fraunhofer CNT

The research and project activities at Fraunhofer CNT are divided into four competence areas. The involved working teams combine scientific knowledge and technical know-how from both industry and research institutions.

| Competence Areas                                                                                                                                                           |                                                                                                                                          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Neue Materialien                                                                                                                                                           | New Materials                                                                                                                            |  |  |

| Entwicklung und Testen neuer Materialkombi-<br>nationen und Schichtsysteme hinsichtlich be-<br>stimmter und vorgegebenen Eigenschaften.                                    | Development and testing of new material and film systems for various applications.                                                       |  |  |

|                                                                                                                                                                            |                                                                                                                                          |  |  |

| Metrologie und Analytik                                                                                                                                                    | Metrology & Analytics                                                                                                                    |  |  |

| Screening neuer Methoden sowie Bestimmung<br>von Schichtparametern und Eigenschaften Inline<br>als auch im Labor anhand von vollständigen<br>Wafern sowie an Bruchstücken. | Screening of new methods to evaluate thin film properties in-line using non-destructive methods or at laboratory scale on wafer coupons. |  |  |

|                                                                                                                                                                            |                                                                                                                                          |  |  |

| Innovative Prozesslösungen                                                                                                                                                 | Innovative Process Technologies                                                                                                          |  |  |

| Forschung und Entwicklung neuer Wege zur<br>Umsetzung der Forschungsergebnisse in der<br>Fertigung, ebenso anhand innovativer Prozess-<br>anlagen.                         | Research and development of new processing methods for production, by using innovative process tools.                                    |  |  |

|                                                                                                                                                                            |                                                                                                                                          |  |  |

| Strukturierung                                                                                                                                                             | Patterning                                                                                                                               |  |  |

| Überprüfung der Funktionalität der Innovationen durch Teststrukturen.                                                                                                      | Verify the innovation's functionality on test structures.                                                                                |  |  |

# Projektübersicht nach Partnern und Fördermittelgebern 2007 Project overview by partners and funding authorities 2007

| project                                                                                                                                                                                                                              | project<br>partner | funding<br>authority |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|

| InnoTech (Förderkennzeichen 10746) Innovative Techniken für kundenspezifische Logikanwendungen in einer DRAM- Umgebung                                                                                                               | Qimonda            | SMWA                 |

| Igel IFD (Förderkennzeichen 10758/1659) Innovative Schichten und Prozesse für zukünftige Mikroprozessor- und Speicherbauelemente mit Strukturen kleiner als 65 nm bzw. Aspektverhältnissen größer 100 nm                             | Qimonda            | SMWA                 |

| Prisma (Förderkennzeichen 11262)<br>Innovative Prozesse für die Grabenisolation mit hohem Aspektverhältnis für sub<br>70 nm Technologien                                                                                             | Qimonda            | SMWA                 |

| Drachen (Förderkennzeichen 11587/1836) Entwicklung von Verfahren und Anlagen zur Siliziumstrukturierung für zukünftige DRAM-Speicherbauelemente mit Aspektverhältnissen >120 bei Strukturbreiten <50nm                               | Qimonda            | SMWA                 |

| Nanosomos (Förderkennzeichen 11451/1807) Vertikale und elektrische Skalierung nitridbasierender, zukünftiger, nichtflüchtiger Speichertechnologien mit minimalen Strukturen                                                          | Qimonda            | SMWA                 |

| Simkon (Förderkennzeichen 01M3183B)<br>Simulationskonzepte für die 32 nm CMOS Technologie                                                                                                                                            | Qimonda            | BMBF                 |

| Switch IFD (Förderkennzeichen 01M3167A) Hochgeschwindigkeitstransistoren für Datenprozessierungschips der Zukunft                                                                                                                    | Qimonda            | BMBF                 |

| Sohar (Förderkennzeichen 01M3171A) Sub 50nm Speicherzellen für Schreib/Lesezyklen im Peta-Bereich                                                                                                                                    | Qimonda            | BMBF                 |

| Nanoanalytik (Förderkennzeichen 13N9432) Nano-Analytik für elektronische Bauelemente mit Strukturen kleiner 40nm                                                                                                                     | Qimonda            | BMBF                 |

| Verbinden / Kuwano (Förderkennzeichen 13N9080 / 13N9082) Verdrahtungstechniken für besondere Geschwindigkeitsanforderungen in flüchtigen Speichern und Mikroprozessoren / Kleinster spezifischer KUpferWiderstand in NANO-leitbahnen | Qimonda<br>AMD     | вмвғ                 |

| Igel AMD (Förderkennzeichen 10772/1659) Innovative Schichten und Prozesse für zukünftige Mikroprozessor- und Speicherbauelemente mit Strukturen kleiner als 65 nm bzw. Aspektverhältnissen größer 100 nm                             | AMD                | SMWA                 |

| Sultan (Förderkennzeichen 11219) Untersuchungen zur SilizierUng von epitaktisch gewachsenen, stark dotierten Silizium-Schichten und Silizium-Legierungen zur Integration von Leistungsfähigeren High-Performance CMOS TrANsistoren   | AMD                | SMWA                 |

| Primer (Förderkenzeichen 11777) Innovative Prozesse zur effektiven Reinigung, Lackentfernung und Reparatur von porösen low-k Dielektrika mit Erprobung der Integrationsfähigkeit                                                     | AMD                | SMWA                 |

| Carat (Förderkennzeichen 12390) Verbesserung der Mikroprozessoreigenschaften mittels Einsatz von Kohlenstoff                                                                                                                         | AMD                | SMWA                 |

| HeiKe (Förderkennzeichen 12419) Untersuchungen zum High-K Metal Gate Stack im 32nm Technologiebereich und darunter                                                                                                                   | AMD                | SMWA                 |

| Switch AMD (Förderkennzeichen 01M3167B) Hochgeschwindigkeitstransistoren für Datenprozessierungschips der Zukunft                                                                                                                    | AMD                | BMBF                 |

| eCMP (Förderkennzeichen 01M3179) Analyse von Oberflächeneigenschaften von Barriere- und Isolatorschichten                                                                                                                            | AMD                | BMBF                 |

| E-Beam Lithographie                                                                                                                                                                                                                  | IMS Chips          | BMBF                 |

### Fraunhofer-Center Nanoelektronische Technologien

## Forschungsschwerpunkte - ausgewählte Beispiele Focus Areas - Selected examples

| Innovative Prozesse & Materialien Innovative Processes and Materials                                                                                                                       |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Metallisierung aus Kupfer für die Höchstintegration                                                                                                                                        | 21 |

| Copper Metallization for very high Integration                                                                                                                                             | 21 |

| Transistorskalierung durch Epitaxie im Kanalbereich<br>Transistor Scaling through Channel Epitaxy                                                                                          | 24 |

| Atomlagenabscheidung zirkoniumbasierter Dielektrika für<br>32 nm DRAM Speicherzellen<br>Atomic layer deposition of zirconium based dielectrics for<br>32 nm DRAM memory cells              | 26 |

| Strukturierung durch Elektronenstrahlverfahren<br>Patterning by E-Beam Lithography                                                                                                         | 28 |

| Spin-Coating in der Halbleiterindustrie<br>Synthese und Ätzverhalten oxidischer Schichten<br>Spin-Coating in the Semiconductor industry<br>Synthesis and etching of new Metal Oxide layers | 30 |

| Metrologie & Analytik<br>Metrology & Analytics                                                                                                                                             |    |

| Röntgenstreumethoden für die Untersuchung von Nanostrukturen X-ray scattering methods for the investigation of nano structures                                                             | 33 |

| Spektroskopie an der atomaren Grenze<br>Spectroscopy at the atomic limits                                                                                                                  | 34 |

| Dynamisches SIMS und TOF-SIMS  Dynamic SIMS and TOF-SIMS                                                                                                                                   | 36 |

| Atomsondentomographie Atom Probe Tomography                                                                                                                                                | 37 |

| TEM - Vom Labor in die Fertigung<br>TEM – from Lab to Fab                                                                                                                                  | 38 |

### Metallisierung aus Kupfer für die Höchstintegration

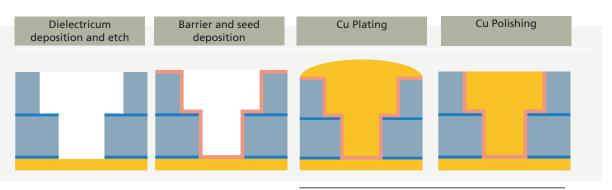

Die Verwendung von Kupfer als Verdrahtungsmaterial hat den Metallisierungsprozess in der Halbleitertechnik revolutioniert und wesentlich dazu beigetragen, schnellere, kleinere und energiesparendere Prozessoren auf den Markt zu bringen. Dieser Fortschritt ist einerseits auf eine veränderte Prozesstechnologie zurückzuführen, die es ermöglicht, komplexe und vielschichtige Verdrahtungsebenen mit gleichbleibender Präzision zu fertigen (Abb. 1). Andererseits sind es die elektrischen Eigenschaften von Kupfer selbst, die zu einer Erhöhung der Prozessorleistung und -zuverlässigkeit führen. Um diese rasante Entwicklung fortzuführen, wird intensiv an neuen Prozessen und Materialien geforscht. Die Arbeiten auf dem Gebiet der Kupfermetallisierung am Fraunhofer CNT konzentrieren sich zurzeit auf die folgenden Problemstellungen.

### Copper Metallization for very high Integration

The use of copper in the semiconductor industry as a wiring material revolutionized the metallization process and contributed substantially to launch faster, smaller and less energy consuming processors (fig. 1). On one hand, this progress can be attributed to changed process technologies, which allow producing more complex multilayered interconnects; and on the other hand to the electrical properties of copper itself which lead to processor performance improvement.

To continue this rapid progress, scientists intensively investigate new processes and materials. The work in the field of copper metallization at the Fraunhofer CNT currently focuses on following areas.

Abb. 1 Prozesskette für die Fertigung einer Kupfer-Verdrah tungsebene fig. 1 process line for the production of cuper wiring layers

#### Der Superfüllmechanismus

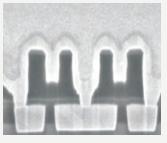

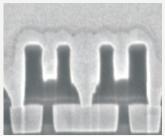

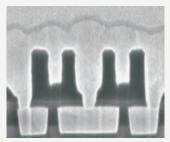

In der Galvanotechnik ist die elektrochemische Herstellung von Kupferschichten, genannt Kupfer-Plating, ein etabliertes und bewährtes Verfahren zur Herstellung hochreiner, kristalliner Kupferüberzüge. Kupfer-Plating ist aber auch das Verfahren erster Wahl bei der Kupferverdrahtung in der Halbleitertechnik. Der Grund dafür liegt darin, dass durch die Zugabe organischer Elektrolytzusätze ein sogenanntes "Super-Filling" erreicht wird. Damit bezeichnet man das von unten nach oben gerichtete Auffüllen von Strukturen, ohne Hohlräume oder Einschlüsse zu verursachen (Abb. 2). Gleichzeitig sorgen die Elektrolytzusätze sowohl für ein polykristallines, nahezu defektfreies Kupferwachstum als auch für eine fast perfekte Nivellierung der Schichtoberfläche. Technologisch ist das Kupfer-Plating ein stabiler und reproduzierbarer Prozess. Allerdings sind das Wirkprinzip der Elektrolytzusätze und die daraus resultierende Kinetik des Cu-Füllprozesses bisher noch weitgehend unverstanden. Eine Klärung des Phänomens "Super-Filling" wäre jedoch wichtig, um die Kupferabscheidung hinsichtlich der elektrischen und mechanischen Eigenschaften des Kupfers weiterzuentwickeln sowie schneller und effizienter an immer kleiner werdende Strukturbreiten anzupassen.

### The copper super fill behavior

The electrochemical deposition of copper films is an established process for the production of ultra-pure crystalline copper for various industrial applications. Copper plating is also the process of choice for producing copper interconnects in integrated circuits. The reason for that is the so-called 'super filling'. Super filling describes the void-free structure filling from the feature bottom towards the feature top (fig. 2). This is enabled by adding organic electrolyte additives. Furthermore, the additives are responsible for a defect-free polycrystalline texture and a nearly perfect leveling of the growing copper film surface.

From the technological point of view, copper plating is a stable and reproducible process. However, from the scientific point of view, the functioning of the additives is still unknown as well as the principles of the super filling. A theory of super filling is required to adapt the plating process efficiently to progressively decreasing interconnect dimensions and to enhance the electrical and mechanical properties of the copper lines.

Abb.2 Cu-Plating "Superfill"-Verhalten: Auffüllen der Strukturen mit Kupfer ohne die Erzeugung von Hohlräumen fig. 2 Cu-plating "superfill"-behavior: cuper Filling of the strucures without creating hollow spaces

### Neue Materialien für die Isolierung der Kupferleitbahnen

Die Linien des Kupfers sind in ein dielektrisches Material eingebettet, welches für die nötige mechanische Stabilität der Verdrahtungsebenen und die elektrische Isolierung zwischen benachbarten Leiterbahnen sorgt.

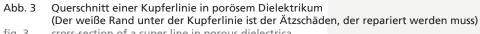

Momentan nutzt man als dielektrisches Material organisch vernetztes SiO<sub>2</sub>, sogenanntes SiCOH. Um jedoch noch dichtere Verdrahtungsstrukturen für immer leistungsstärkere Prozessoren zu erreichen, müssen die kapazitiven Effekte zwischen den Kupferlinien noch weiter eingedämmt werden. Daher geht der Trend dahin, Luft – nach Vakuum das ideale dielektrische Material – zu integrieren. Der Einsatz von Luft als isolierendes Material kann realisiert werden, indem man nanoporöse, also mit Luftporen versehene, SiCOH-Materialien fertigt. Die Integration solch nanoporöser Materialien ist wegen ihrer hohen Empfindlichkeit bei Strukturierungs- und Reinigungsprozessen eine technologische Herausforderung. Besonders das Strukturätzen mit Hilfe hochenergetischer Plasmen führt zu einer Schädigung der Oberfläche, was sich wiederum in einer schlechteren Isolationswirkung äußert (Abb. 3). Es wird daher intensiv an der Entwicklung geeigneter Prozesse geforscht, um die Poren an der Oberfläche zu versiegeln und die geschädigte Oberfläche zu reparieren.

New materials for copper isolation

The copper wiring is embedded into a dielectric material, which is responsible for the mechanical stability of the interconnects and the electrical insulation between adjacent copper lines. Currently, carbon doped SiO<sub>2</sub>, so called SiCOH, is used. However, to achieve even more compact wiring structures for more powerful processors, the capacitance between the copper wires must be further reduced. Hence, there is a tendency of integrating air – after vacuum the perfect isolator material - into the dielectric film. This is realized by the introduction of nano pores into the SiCOH film. The integration of nano porous materials is a technical challenge due to the high sensitivity to the etch and cleaning processes. Especially patterning with high energetic ion bombardment damages the surfaces, which results in a decreased electrical isolation (fig. 3). Therefore, intensive research is carried out to investigate feasible surface treatment and sealing processes.

fig. 3 cross-section of a cuper line in porous dielectrica (the white border below the cuper line is the etch damage which have to be repared)

### Erprobung innovativer Prozesstechnologien

Als Grenzschicht zwischen Dielektrikum und eingebetteten Kupferbahnen befindet sich eine dünne Barriere von einigen nm Dicke, die verhindert, dass Kupfer in das Dielektrikum diffundiert. Die Anforderungen an diese Barriereschicht sind hoch. Sie muss eine sehr gute Haftung sowohl zum Dielektrikum als auch zum Kupfer besitzen ohne Phasengemische zu bilden, und sie muss so dünn und dicht wie möglich sein. Als optimal hat sich dafür eine TaN/Ta-Doppelschicht erwiesen, die mit Hilfe von physikalischer Gasphasenabscheidung (PVD - physical vapor deposition) abgeschieden wird. Allerdings ist bei PVD-Verfahren die Schichtdickenverteilung in Strukturen allgemein schlecht einstellbar. Je kleiner die Strukturen werden, desto schwerer könnte dieser Nachteil wiegen.

Daher wird versucht, rechtzeitig alternative Beschichtungsverfahren zu evaluieren. Hohes Potenzial hat die Atomlagenabscheidung (ALD), die zu einer konformen Bedeckung auch in Strukturen mit hohem Aspektverhältnis führt. Die Herausforderung besteht momentan darin, die organische Kontamination der TaN/Ta-Schichten zu eliminieren und die Adhäsion zu Dielektrikum und Kupfer zu verbessern (Abb. 4).

### Evaluating new process technologies

A barrier layer between the dielectric material and the embedded copper of some nm thickness prevents the copper from diffusing into adjacent materials. The quality requirements for barrier layers are high. For instance, a strong adhesion of the barrier layers to both the dielectric and copper without forming alloys is required. At the same time, barrier films need to be as thin as possible. A TaN/Ta double layer, deposited by a PVD process (PVD - physical vapor deposition), was found to be an optimal system fulfilling those demands. Difficulties may arise when the feature sizes become smaller and smaller, as it gets harder to achieve thin and conformal layers inside high aspect ratio features with PVD. Therefore, the evaluation of other deposition techniques is in progress. In that context, ALD (atomic layer deposition) is a promising technique to achieve uniform coverage even inside features with high aspect ratios. The challenge of ALD processes is to eliminate organic contaminations of the TaN/Ta-layers and to improve the adhesion of the barrier material to the dielectric and copper material (fig. 4).

### Anwendungsbezogene Optimierung und Zuverlässigkeitsprüfung

Auf einer Prozessorfläche von 1 cm² beträgt die Gesamtlänge der Kupferverdrahtung derzeit ca. 3 km mit steigender Tendenz. Kleine Änderungen der Materialeigenschaften können daher große Auswirkungen auf Performance, Geschwindigkeit und Energieverbrauch von Prozessoren haben. Daher wird versucht, die Gefügestruktur des Kupfers nach dem Kupfer-Plating durch Temperprozesse zu beeinflussen, um durch Wärmezufuhr ein Ausheilen von Gitterfehlern sowie Kornwachstum und Stressabbau zu erreichen. Das hilft, die Stabilität und die elektrische Leitfähigkeit der Kupferleitbahnen zu erhöhen.

Zudem ist es wichtig, das Zusammenwirken der verschiedenen Materialien (Dielektrikum, Barriereschicht und Kupfer) zu charakterisieren, um mechanische Spannungen zu verhindern. Dafür ist es unerlässlich, Belastungstests durchzuführen, Schwachstellen zu erkennen und Prozessschritte zu optimieren. Auch bei immer kleiner werdenden Strukturen und komplexerer Prozesstechnologie muss die Zuverlässigkeit der Schaltungen gewährleistet sein.

### Optimization of Application and Reliability Tests

Today, a processor die contains about 3 km of copper interconnects on 1 cm<sup>2</sup> with increasing tendency. Small changes in material properties are influencing the performance and power consumption of processor dies. Therefore, thermal annealing is used to control the copper grain structure after electrochemical plating. Annealing causes grain growth and a reduction of lattice defects. Thus, the electrical conductivity and reliability of copper interconnects can be enhanced. To minimize stresses in the interconnects, the interactions of dielectric, barrier layer and copper have to be characterized. Stress migration tests help to identify weak points and are used to optimize process steps. Even with ever shrinking structures and an increasing complexity of process technologies the reliability of devices has to be guaranteed.

### Transistorskalierung durch Epitaxie im Kanalbereich

Mit dem Übergang der Mikro- in die Nanoelektronik bewegen sich die Größenverhältnisse immer mehr in Richtung atomarer Abmessungen. Eine Erhöhung der Schaltgeschwindigkeiten der Transistoren gestaltet sich immer schwieriger, da gleichzeitig Leckströme und parasitäre Widerstände überproportional zunehmen.

Um diese Leistungslücke der Siliziumchips zu schließen, halten in der Halbleiterindustrie fortwährend neue Materialien und Verfahren Einzug. Eine Problematik, an der zurzeit am Fraunhofer CNT in Kooperation mit AMD geforscht wird, ist die mechanische Verspannung des Transistorkanals von MOSFETs. Durch das Einwirken von Zug- bzw. Druckspannungen auf den Transistorkanal lässt sich die Mobilität von Elektronen bzw. Elektronenlöchern gezielt erhöhen, was leistungsfähigere als auch sparsamere Siliziumchips ermöglicht. Hierfür bieten sich unterschiedliche Verfahren an,

Hierfür bieten sich unterschiedliche Verfahren an, wie z.B. global verspannte Substrate, kompressive und tensile Nitridschichten oder der Stress Memory Effekt. Am Fraunhofer CNT werden im Rahmen diesen Forschungsprojektes neuartige Epitaxieverfahren zur Erzeugung von verspannten Transistorkanälen untersucht.

### Transistor Scaling through Channel Epitaxy

When going from micro to nano scaled devices, atomic dimensions are approached. Further decreasing the delay time of transistors becomes more and more difficult, as at the same time leakage currents and parasitic resistivities increase exponentially.

To overcome the scaling issue, the semiconductor industry is perpetually searching for new materials and processes. One topic, that is currently investigated at the Fraunhofer CNT in cooperation with AMD, is the mechanical stressing of the transistor channel of MOSFETs. Due to the influence of tensile and compressive stresses on the transistor channel, the mobility of electrons and electron holes can be increased, respectively. That allows the production of silicon devices with a higher performance and less energy consumption. Various approaches like strained substrates, strained nitride layers, and stress memorization techniques are utilized to manufacture microprocessors. Within these research project, the Fraunhofer CNT evaluates innovative epitaxial deposition techniques.

The recessed area is filled with

SiGe or Si:C via a selective epitaxy process. The material grows only

on open silicon areas, but not on Recess of the source- and drain silicon nitride or oxide. The lattice mismatch between Si and SiGe resp. region by anisotropic reactive ion etching (RIE) Si:C causes the mechanical strain of Transistor condition in the transistor channel the beginning Gate Elektrode Gate electrode Etch back Herausatzen Gateoxid Gate oxide of Silicon des Silzium SiGe bzw. Si:C SiGe or Si:C Drain Source (a) (c) (b)

Abb. 5 Schematische Darstellung des SiGe bzw. Si:C Prozesses fig. 5 Schematic Illustration of the SiGe or Si:C Prozess

Bei der Abscheidung unterschiedlicher, aufeinanderliegender Materialien (Heteroepitaxie) erzeugen die verschiedenen Gitterkonstanten mechanische Spannungen. In Silizium-Germanium (SiGe) erhöht der Einbau von Germanium die Gitterkonstante, während in Kohlenstoff dotiertem Silizium (Si:C) der Einbau von Kohlenstoff die Gitterkonstante verkleinert. Erst seit kurzem findet die SiGe Epitaxie in der CMOS Technologie Anwendung. Dabei werden die Source- und Draingebiete der Transistoren herausgeätzt und im Anschluss epitaktisch mit SiGe oder Si:C wieder gefüllt (Abb. 5). Die Art der

During the stacking of different film materials (hetero epitaxy) the different lattice constants create mechanical stresses. In the material combination silicon-germanium (SiGe) the implanted germanium atoms cause a higher lattice constant, while in carbon doped silicon (Si:C) the implanted carbon atoms lead to a lower lattice constant compared to a pure silicon lattice.

The SiGe epitaxy has recently entered the CMOS technology. For the SiGe epitaxy, the transistor source and drain regions are formed by etching and refilled with epitaxially grown SiGe or Si:C.

Transistoren bestimmt hierbei die Materialauswahl, der pMOS, dessen Leitfähigkeit durch Löcher bestimmt wird, bevorzugt Druckspannungen, die durch SiGe eingeprägt werden. Mit Hilfe der Epitaxie von kohlenstoffdotiertem Silizium können auf analoge Weise Zugspannungen im Kanal von nMOS-Transistoren erzeugt werden, um so die Beweglichkeit der Elektronen zu erhöhen. Aktuelle Forschungsschwerpunkte am Fraunhofer CNT im Bereich der Epitaxie sind sowohl SiGe-Epitaxie als auch die Si:C-Epitaxie.

#### Epitaxieverfahren für Si:Ge und Si:C

In der Industrie, z.B. bei AMD und IBM, wird SiGe heute mittels der chemischen Niederdruck-Gasphasen-Epitaxie (low pressure chemical vapor deposition - LPCVD) bei typischen Reaktionstemperaturen um 700°C abgeschieden. Um die mechanische Spannung im Transistorkanal weiter zu erhöhen, kann man durch den Einbau von mehr Germanium die Gitterfehlpassung zwischen Si und SiGe vergrößern. Für den größtmöglichen Spannungsübertrag in den Transistorkanal müssen Kristalldefekte vermieden werden, die schon bei der Schichtabscheidung erzeugt werden. Im Fraunhofer CNT wird deshalb der Abscheidungsprozess in einem Ultra Hochvakuum System erforscht (UHV-CVD). Durch die Reduzierung des Prozessdruckes sowie Verwendung neuer Prozessgase lässt sich die Reaktionstemperatur deutlich senken. So können Schichten mit Ge-Gehalten bis 40% selektiv abgeschieden werden.

Die Hauptschwierigkeit bei der Si:C Epitaxie liegt in der geringen Löslichkeit von Kohlenstoff in Silizium. Im chemischen Gleichgewicht lösen sich nur 0,0004% Kohlenstoff im Siliziumgitter. Für eine ausreichende Verspannung des Transistorkanals müssen mindestens 1 bis 2% Kohlenstoff auf den Gitterplätzen eingebaut werden. Um diese hohe Konzentrationen zu erreichen, wird am Fraunhofer CNT ein UHV-CVD System eingesetzt, mit dem Schichten im chemischen Ungleichgewicht bei möglichst niedrigen Temperaturen abgeschieden werden können. Die niedrige Abscheidungstemperatur verringert die Diffusion der Kohlenstoffatome und garantiert, dass die Atome auf thermodynamisch metastabilen Gitterplätzen eingeordnet werden. Auf diese Weise ist es gelungen, verspannte Si:C Schichten mit Kohlenstoffkonzentrationen nahe 2% zu erzeugen.

Hereby, the kind of transistor defines the choice of material: For p-MOS, where current is conducted by electron holes, compressive strain is required and realized by SiGe epitaxy (fig. 5). For n-MOS, the application of Si:C is preferred to achieve tensile stress, which improves the electron mobility. Current research activities in the field of epitaxy at the Fraunhofer CNT are carried out for both, SiGe and Si:C.

### Epitaxy for Si:Ge and Si:C

Semiconductor manufacturers like AMD and IBM are performing SiGe epitaxy by low pressure chemical vapor deposition (LPCVD) typically at process temperatures around 700°C.

In order to further increase the mechanical strain in the channel, the lattice mismatch between Si and SiGe can be enlarged by increasing the Ge content. For a maximum strain transfer into the transistor channel, crystal defects, which are created during the film growth, must be avoided.

Therefore, the Fraunhofer CNT is testing an utra high vacuum (UHV) CVD system as innovative deposition technique. Due to the reduced process pressure and the use of new process gases, the reaction temperature can be decreased significantly. That allows the deposition of epitaxial layers with Ge concentrations of up to 40%.

The main challenge in the Si:C epitaxy is the very low solid solubility of carbon in silicon. In chemical equilibrium, only 0.0004% carbon atoms are incorporated into the silicon lattice. For a sufficient tension of the transistor channel, at least 1 to 2% carbon must be incorporated.

To reach those high concentrations, an UHV-CVD system is used at the Fraunhofer CNT. That allows a layer deposition in chemical non-equilibrium at lowest possible temperatures.

Low deposition temperatures reduce the diffusion of the carbon atoms and guarantee the incorporation of the thermodynamically metastable lattice sites. That way it was possible to create strained Si:C layers with carbon concentrations close to 2%.

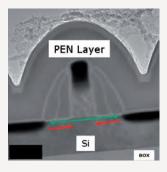

### Atomlagenabscheidung zirkoniumbasierter Dielektrika für 32 nm DRAM Speicherzellen

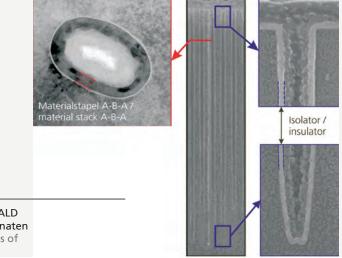

Mit zunehmender Miniaturisierung integrierter DRAM Speicher wachsen die Herausforderungen in nahezu allen Bereichen des mehr als 600 Prozessschritte umfassenden Herstellungsprozesses für einen Speicher. Ein wesentliches Gebiet aktueller Forschung, das in Zusammenarbeit mit Qimonda bearbeitet wird, ist die Entwicklung neuartiger Dielektrika für Speicherzellen der zukünftigen 32 nm Generation mit Grabenarchitekturen (engl.: Deep Trench, DT). Bei diesen gilt es, dreidimensionale Strukturen mit einem Aspektverhältnis von bis zu 100:1 konform zu beschichten, was nur durch die innovative Technologie der Atomlagenabscheidung (engl.: atomic layer deposition, ALD) möglich ist. Kennzeichnend für ALD Prozesse ist die kontrollierte, gepulste Abscheidung einzelner Komponenten, Atomlage für Atomlage in einem selbstlimitierenden Wachstumsprozess.

Ein Zyklus zur Abscheidung einer Atomlage des typischerweise verwendeten Metalloxid-Dielektrikums umfasst die Schrittfolge: Puls des Metallausgangsstoffs - Inertgasspülen – Puls der sauerstoffhaltigen Komponente – Inertgasspülen (Abb. 6). Durch die Abscheidung der Atomlagen werden exzellente Homogenität einer ALD-Schicht in einer DT Struktur sowie Schichtdesigns, wie z.B. Laminatstrukturen möglich gemacht

Atomic layer deposition of zirconium based dielectrics for 32 nm DRAM memory cells

With further shrinking of integrated DRAM memories, challenges arise in almost all of the more than 600 process steps of a manufacturing line for memories. One topic of the current research at the Fraunhofer CNT in cooperation with Qimonda is the development of new dielectric materials for memory cells of the 32 nm generation containing deep trench capacitors. These capacitors, which are three dimensional structures with an aspect ratio of up to 1:100, need to be coated conformally. That can only be achieved by an innovative technique called atomic layer deposition (ALD). A characteristic feature of ALD is the controlled deposition of a single atomic layer during a self limited growth cycle.

A deposition cycle of one atomic layer of a commonly used metal oxide dielectric consists of the following steps: a pulse of the metal containing chemical, purge with inert gas, a pulse of an oxygen containing gas, purge with inert gas (fig. 6). Perfect homogeneity of an ALD film in a deep trench structure as well as a laminate structure can be produced by using ALD.

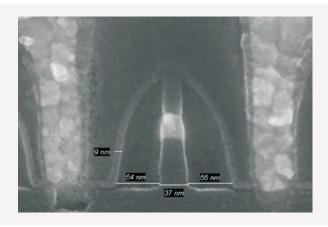

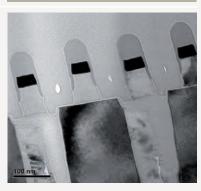

Abb. 6 TEM Aufnahmen an DT Strukturen: Möglichkeiten der ALD zur konformen Beschichtung und Herstellung von Laminaten fig.6 TEM images of DT structures: potential of ALD processes of conformal deposition and laminate films

Um eine möglichst große Zahl an potentiellen Speichermaterialien über ALD herzustellen und die anschließend aussichtsreichsten davon im Produktkreislauf zu testen, stehen am Fraunhofer CNT zwei Anlagen zur Verfügung. Eine Forschungsanlage für 300 mm Scheiben der Firma FHR, einem Anlagenbauer aus Sachsen, die in Zusammenarbeit mit dem Fraunhofer IKTS betrieben wird, dient dabei der Einführung neuer Materialien und der Auswahl der für die Produktion am besten geeigneten Chemikalien sowie der Weiterentwicklung des ALD-Prozesses auf technologischer Seite. Diese Anlage ist daher mit variablen Prozesskammern ausgestattet

There are two ALD tools available at the Fraunhofer CNT for studying a large number of potential materials and to test the most promising candidates in a production cycle. In cooperation with the Fraunhofer IKTS a 300 mm research tool manufactured by a local company FHR (Saxony) is used to introduce new materials. It is used for the selection of chemicals suitable for production and the improvement of the ALD process from a technological point of view. The tool is equipped with variable process chambers and a gas system which enables the use of many different chemicals (fig. 7). The second tool is made by Jusung (Korea) and

und besitzt ein Gasversorgungssystem, welches für eine Vielzahl von Chemikalien ausgelegt ist (Abb. 7). Eine zweite, produktionsnahe Anlage der Firma Jusung, aus Korea zeigt das Prozessmodul wie auch den schematischen Aufbau - hier werden in Kooperation mit dem Fraunhofer IISB die ausgewählten Materialien mit der zugehörigen Chemie für die Herstellung produktionsnaher Bauelementstrukturen eingesetzt und über kleine Änderungen am vorentwickelten Prozess weiter optimiert, um die notwendigen elektrischen Kenngrößen eines DRAM's der zukünftigen Generation zu erreichen. Bereits kleinste Schwankungen im Prozess haben dabei große Auswirkungen auf die Materialeigenschaften, weshalb die eingesetzte Anlage vor allem eine ausreichende Prozessstabilität gewährleisten muss. Der Vorteil der industrienahen Umgebung ergibt sich hier direkt aus der Zulieferung der DT Strukturen und der sofortigen Weiterprozessierung der beschichteten Halbleiterscheiben, hin zu fertigen Teststrukturen, durch den Industriepartner sowie durch umfangreiche Analysemöglichkeiten vor Ort.

Der Isolator ZrO, gilt aufgrund seiner hohen Dielektrizitätskonstante ε als aussichtsreiches Speicherdielektrikum für DRAM Speicherzellen. Dabei stehen nicht nur die reine Optimierung sondern vor allem die grundlegenden Eigenschaften des Materials im Focus. Denn das ist die entscheidende Voraussetzung für das Verständnis des Einflusses nachfolgender Prozesse auf Struktur und Eigenschaften der Schicht und auf das Verhalten im Verlauf ihrer Lebenszeit in einem Speicherchip. Die bisherigen Ergebnisse zeigen, dass sich ZrO, sehr konform mittels ALD in deep trenches abscheiden lässt und dass sehr gute elektrische Kennwerte wie hohe Kapazität und niedriger Leckstrom erreicht worden sind. Jedoch bleiben diese Eigenschaften des reinen ZrO<sub>3</sub> in kompletten Bauelementstrukturen und nach thermischen Behandlungen, wie sie in Folgeprozessen immer auftreten, nicht stabil. Es hat sich gezeigt, dass Dotierungen in Form von Mischoxiden oder Laminaten das Material stabilisieren können. Die Optimierung der Zusammensetzungen, ideale Schichtstapel sowie deren intensive physikalische und elektrische Charakterisierung stehen im Mittelpunkt der aktuellen Forschungen auf dem Gebiet der hoch-ε Schichten und der ALD Prozesse. Daneben wird aber schon jetzt mit der Arbeit an Materialkonzepten für die übernächsten DRAM-Generationen begonnen.

operated in cooperation with Fraunhofer IISB. The previously selected materials and the corresponding chemistry are used in this tool to manufacture structures which are very similar to those used in the real device. The materials are optimized by slight adjustments of the previously developed process in order to fulfill the electrical specifications of future DRAM generations.

As the slightest variations of the process parameters can have an impact on material properties, the used tool needs to provide highest process stability. Currently, the isolator ZrO<sub>3</sub> is investigated mainly because of its high dielectric constant k which makes it a promising material for DRAM memory cells. The focus is not only to optimize but also to study the fundamental material properties. This is required to understand the influence of subsequent processes on the film structure, stability and the behavior during the life time of the chip. So far, results indicate that ZrO<sub>2</sub> can be deposited very conformal in deep trenches and that very good electrical properties like large capacities and small leakage currents can be achieved.

However, these properties of pure ZrO<sub>2</sub> are unstable in complete device structures especially after thermal treatments which occur in the following process steps. It turns out that doping in the form of mixed oxides or laminates can stabilize the material. The optimization of the composition, ideal stacks and their intensive physical and electrical characterization are the main focus of current research in the field of high k films and ALD processes. Besides, the development of new material concepts for the next DRAM generations has already been started.

Gesamtansicht der im Fraunhofer CNT-Abb. 7 Reinraum installierten ALD-Forschungsanlage fig. 7 View on research ALD-tool (FHR) installed in the Fraunhofer CNT clean room

27

### Strukturierung durch Elektronenstrahllithographie

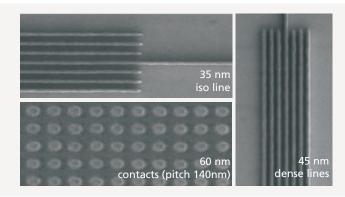

Um äußerst feine Strukturen im Bereich von derzeit 50 nm bis 40 nm und weniger für integrierte Schaltkreise herzustellen, kann die Elektronenstrahllithografie als spezielle Technologie eingesetzt werden. Dabei wird ein Wafer mit einem elektronenempfindlichen Lack - "photo resist" - beschichtet und ein Elektronenstrahl rastert dessen Oberfläche mit einer Energie von 50keV ab. Durch diesen Prozess wird an den bestrahlten Stellen der Lack chemisch verändert und ein latentes Bild im Lack erzeugt. Der Lack wird entwickelt. Abhängig davon, ob der zumeist chemisch verstärkte Lack negativ oder positiv ist, bleibt entweder Material stehen oder wird entfernt. Die gewünschte Struktur wird somit im Lack fixiert und es können weitere Bearbeitungsschritte wie Ätzen oder Implantation erfolgen.

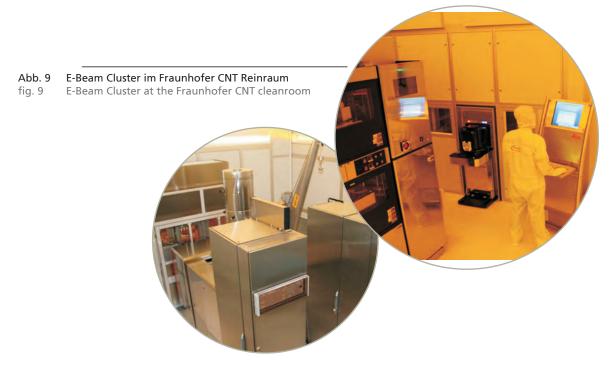

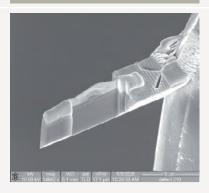

Das Fraunhofer CNT verfügt über einen Formelektronenstrahlschreiber ("Variable Shaped Beam") mit der elektronen-optischen Säule SB3050DW der Vistec Electron Beam GmbH sowie über ein TEL Clean Track ACT-12 zur Belackung und Durchführung verschiedenster Temperaturschritte und Entwicklung (Abb.9/10).

Die Bereitstellung der Prozesse, Aufbereitung der Layoutdaten sowie die Integration in existierende Waferflows (optische Lithografie, Ätzen) gehören zum Aufgabengebiet des Teams "Center of Competence E-Beam", ebenso wie der Betrieb des E-Beam-Schreibers. Für diese Arbeiten wird ein reger Austausch mit Einrichtungen wie IMS Chips - Stuttgart, LETI - Grenoble als anderen Partnern nationaler und europäischer Förderprojekter, gepflegt.

### Patterning by E-Beam Lithography

Electron beam lithography as a special technology can be applied to create extremely fine structures for integrated circuits in the present range of 50 nm to 40 nm and even below. In that technique, a wafer is coated with an electron sensitive photo resist and an electron beam scans the surface with a typical energy of 50 keV. At the exposed sites, the resist is chemically changed by that energy and a latent image is generated in the resist layer. Subsequently, the resist is developed. Depending on the negative or positive behavior of the chemically amplified resist, the exposed material remains on the wafer or it is removed. That way, the desired structures are fixed in the resist and further processing steps such as etching or implantation can take place. A variable shaped electron beam writer with an electron optical column SB3050DW of Vistec Electron Beam GmbH is installed at the Fraunhofer Center for Nanoelectronic Technologies, as well as a TEL Clean Track ACT-12 tool for coating, temperature conditioning and development steps (fig. 9/10).

The E-Beam writer is operated by the "Center of Competence E-Beam", a team at the Research & Development Center of Qimonda Dresden GmbH & Co. OHG. Further responsibilities of the team are allocation of the processes, the preparation of the layout data as well as the integration in existing wafer flows (optical lithography, etching). For their work, an active exchange with external research institutes like IMS Chips, Stuttgart and Leti, Grenoble as well as partners in international and European funding projects is maintained.

Abb. 10 Auflösung der SB3050DW-Säule mit einem chemisch verstärkten Lack fig. 10 SB3050DW-column resolution with a chemical intensified resist

Elektronenstrahl-Direktschreiben ist eine äußerst flexible Lithografielösung, da zum Testen verschiedenster Designvariationen kein teurer Maskensatz gekauft werden muss. Die Belichtungsdaten werden in diesem Prozess datentechnisch gesondert behandelt und direkt auf den Wafer geschrieben (Abb. 11). Trotz längerer Schreibzeit lassen sich somit die Durchlaufzeiten verkürzen und wertvolle Entwicklungszeiten einsparen.

Durch ihre hohe Auflösung ist die Elektronenstrahllithografie der optischen Lithographie im Entwicklungsstadium voraus, welches sich als großer Vorteil erweist. Dadurch können auch verschiedenste

Schaltungskonzepte der modernsten Speichertechnologie erprobt werden. Zukünftig ist der Einsatz

der E-Beam Technologie auch bei der Chip-Personalisierung und der kundenspezifischen Strukturierung denkbar. Durch die besondere Aufstellung des

Fraunhofer CNT im Hinblick auf Reinraumanbindung und Workflow war es bereits möglich, ganze

Transistorebenen oder Teile davon mit Elektronenstrahl zu strukturieren und in den Fertigungsablauf

von Qimonda exemplarisch zu integrieren.

Electron beam direct writing is a very flexible lithography method, as for testing of several design variations no expensive set of masks has to be purchased. From a technological point of view the exposure data is handled separately and directly written onto the wafer (fig. 11). Despite longer writing times a reduction of the cycle time and valuable development time is achieved.

A further advantage is the above mentioned high resolution of the process, which gives electron beam lithography an edge over the optical lithography in the development stage. Thus, several circuit concepts of the latest memory technologies can be tested. In the future, further fields of application could be chip personalization and customer specific structuring. Because of the special assembly of the Fraunhofer CNT regarding clean room connection and workflow, it had been possible to structure whole transistor levels or parts of it by electron beam and to integrate them in the manufacturing examplarily, already.

Abb. 11 Mit E-Beam belichtetes, voll integriertes DRAM-Gate fig. 11 Via E-Beam exposed, full integrated D-RAM Gate

### Spin-Coating in der Halbleiterindustrie Synthese und Ätzverhalten oxidischer Schichten

Im Rahmen der Forschungsarbeit wird mit einer speziell hergestellte Lösung aus chemischen Precursoren, dem Sol gearbeitet. Diese Lösung wird mittels Spin-Coating, über eine sich drehende Scheibe auf Si-Wafer mit einem Durchmesser von 300 mm aufgebracht (Abb. 12). Dabei werden Viskosität und Benetzbarkeit mit Hilfe von Additiven an die Anforderungen der Hersteller angepasst. Durch diesen Herstellungsprozess können Probleme wie Porosität, Rissbildung und zu starke mechanische Belastung des Wafers über eine spezielle Temperaturführung bei der Ausheilung der Schicht vermieden werden. Die Vorarbeiten für diesen Prozessschritt wurden am Fraunhofer Institut für Keramische Technologien und Systeme (IKTS) für Wafer mit 100 mm Durchmesser durchgeführt.

Spin-Coating in the Semiconductor industry - Synthesis and etching of new Metal Oxide layers

Within the scope of that work specially manufactured solutions from chemical precursors, called Sols, are used. That solution is applied onto a 300 mm silicon wafer by the spin-coating technique (fig. 12).

The viscosity and wettability is adjusted to the requirements by using additives. Incidental porosity, cracking and strong mechanical stress of the wafer can be avoided by applying a special temperature regime during processing. The preliminary work was carried out at the Fraunhofer Institute for ceramic technologies and systems (IKTS) on 100 mm wafers

| Application & Spin-Coating | Condensation<br>350°C | Polymerisation<br>700°C |

|----------------------------|-----------------------|-------------------------|

| 1                          |                       |                         |

| -                          | \$555                 | -                       |

Abb. 12 Schematische Darstellung des Spin Coating fig. 12 Schematic diagram of the Spin-Coating process

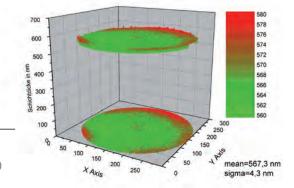

Als ausschlaggebende Kriterien zur Optimierung der ZrO, Schichten gelten dabei die Homogenität (Abb. 13) und Defektfreiheit der herzustellenden Schicht sowie ein geringer mechanischer Stress des Substrates. Aus ökonomischer Sicht ist besonders eine Optimierung der Technologie zur Herstellung der Schichten mit einer Dicke von 400 nm wichtig. Diese können mit einer doppelten Beschichtung erreicht werden.

Das einfache und kostengünstige Verfahren der Spin-Coating-Technik zeichnet sich durch eine homogene Verteilung der Ausgangsstoffe sowie eine hohe chemische Reinheit aus.

Die so erzeugten Schichten können unter anderem als Hartmasken für Deep-Trench-Ätzprozesse Anwendung finden. Durch höhere Resistenz gegenüber den Ätzgasen als zurzeit verwendetes Siliziumdioxid kann die Schichtdicke der Hartmasken um mindestens die Hälfte reduziert werden.

Durch die hierdurch erreichten Möglichkeiten Zeit und Geld einzusparen, wird der Fertigungsprozess zusätzlich positiv beeinflusst.

The important criteria for the optimization of the zirconium oxide layers are the uniformity (fig. 13), a low level of defects and a low mechanical film stress. An optimization of the deposition technology is necessary to reach a 400 nm film thickness. That thickness, which is important for economic reasons, can be achieved by double coating. The very simple and relatively cheap method of spin-coating is characterized by a homogeneous distribution of the raw materials and a high chemical purity.

The layers obtained in such a way can be used as hard masks for deep trench etching processes. Because of a higher resistance to the etching gases, compared to the state of the art silicon dioxide masks, the layer thickness of the hard masks can be reduced by at least 50 percent. That fact is very beneficial for the production process and thus opens up the possibility for manufacturers to save time and money.

Abb. 13 Abbildung der Schichtdicke eines Wafers nach Temperung bei 350°C

fig. 13 Thickness mapping of a pre-annealed wafer (350°C)

Metrologie & Analytik\_\_\_\_\_ Metrology & Analytics

### Röntgenstreumethoden für die Untersuchung von Nanostrukturen

Der Kompetenzbereich Metrologie & Analytik des Fraunhofer CNT ist ein wichtiger Zwischenstop für die Entwicklung vieler Prozessschritte und Bearbeitungsmethoden. In diesem Bereich ist es den Wissenschaftlern möglich, einzelne Materialien und Schichten auf Eigenschaften wie Dichte, Zusammensetzung oder Rauhigkeit hin zu prüfen. Nach Erhalt ihrer Ergebnisse können die einzelnen Fachabteilungen ihre Prozesse optimaler auf die Materialien und deren Reaktionen anpassen und somit effektiver produzieren.

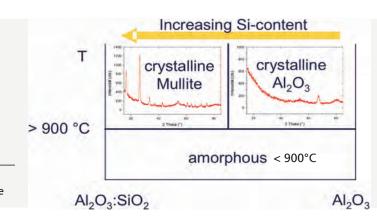

Eine wichtige Methode zur Charakterisierung von high-k Materialien ist zum Beispiel der Einsatz von Röntgenstreumethoden wie X-Ray-Diffraction (XRD) und X-Ray-Reflectivity (XRR). Dabei wird vor allem der Einfluss verschiedener Abscheidungsparameter auf die Struktur der Waferschichten untersucht, um so den Abscheidungsprozess zu optimieren bzw. um geeignete Prozessfenster zu definieren. So wurde beispielsweise die Phasenbildung von AlSiO<sub>x</sub>-Schichten in Abhängigkeit vom Si-Anteil und der Temperatur einer nachfolgenden Wärmebehandlung untersucht. Die Al-reichen Dünnschichtsysteme kristallisieren nach einer Wärmebehand-

lung von über 900°C in der n-Al<sub>2</sub>O<sub>2</sub> Phase, einer

Mullitstruktur beobachtet (Abb. 1).

kubischen Defektspinell-Struktur. Mit steigendem

Si-Anteil wird dann der Umschlag in die silikatische

Die Kristallisationstemperatur der Schichten ist unter anderem von deren Dicken abhängig. Mittels der XRR-Methode konnte nachgewiesen werden, dass mit dem Übergang der Atomanordnungen von einem amorphen zu einem kristallinen Zustand einerseits die Schichtdicke schrumpft und andererseits die Dichte des Materials ansteigt. Dies äußert sich in einem größeren Abstand der Schichtdickenoszillationen sowie einem geringfügig erhöhten Wert des kritischen Winkels für die kristallinen Schichten. Für die genaue Bestimmung der Werte für Dicke, Dichte und Rauhigkeit wird ein Schichtmodell an die Messung angepasst. Eine Simulation des Spektrums verwendet die gesuchten Parameter zum Anpassen des theoretischen Modells an das gemessene Spektrum.

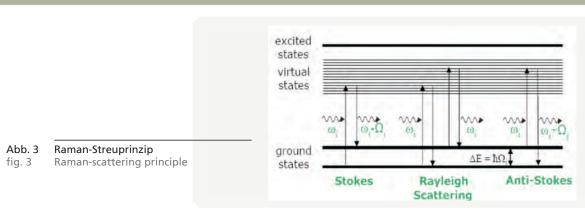

### X-ray scattering methods for the investigation of nano structures

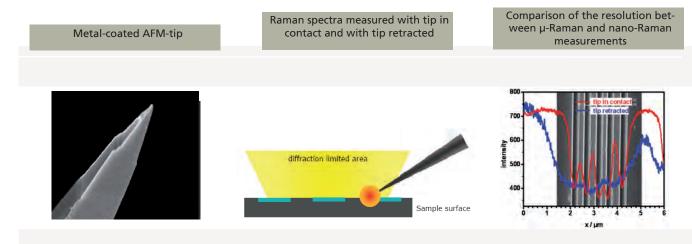

In the Fraunhofer CNT, Metrology & Analytics is an important intermediate stop in the development of a wide variety of process steps and methods. In this department the scientists are able to investigate the thickness, composition or roughness of different materials and layers. After receiving analytical results, the individual departments can ideally match their processes to the materials and their reactions in order to produce more effectively. For instance, an important method for the characterization of high k materials is the application of X-ray scattering methods like XRD and XRR. Those are used especially for the investigation of the influence of different deposition parameters on the film structure in order to optimize the deposition process and/or to define suitable process windows.